# **Timers and STM32** How to learn fast and stay sane

## PIOTR SUWAŁA / REGULAR JAVA DEVELOPER

### HIDDEN AGENDA

# - STM32/GENERIC TOOLING

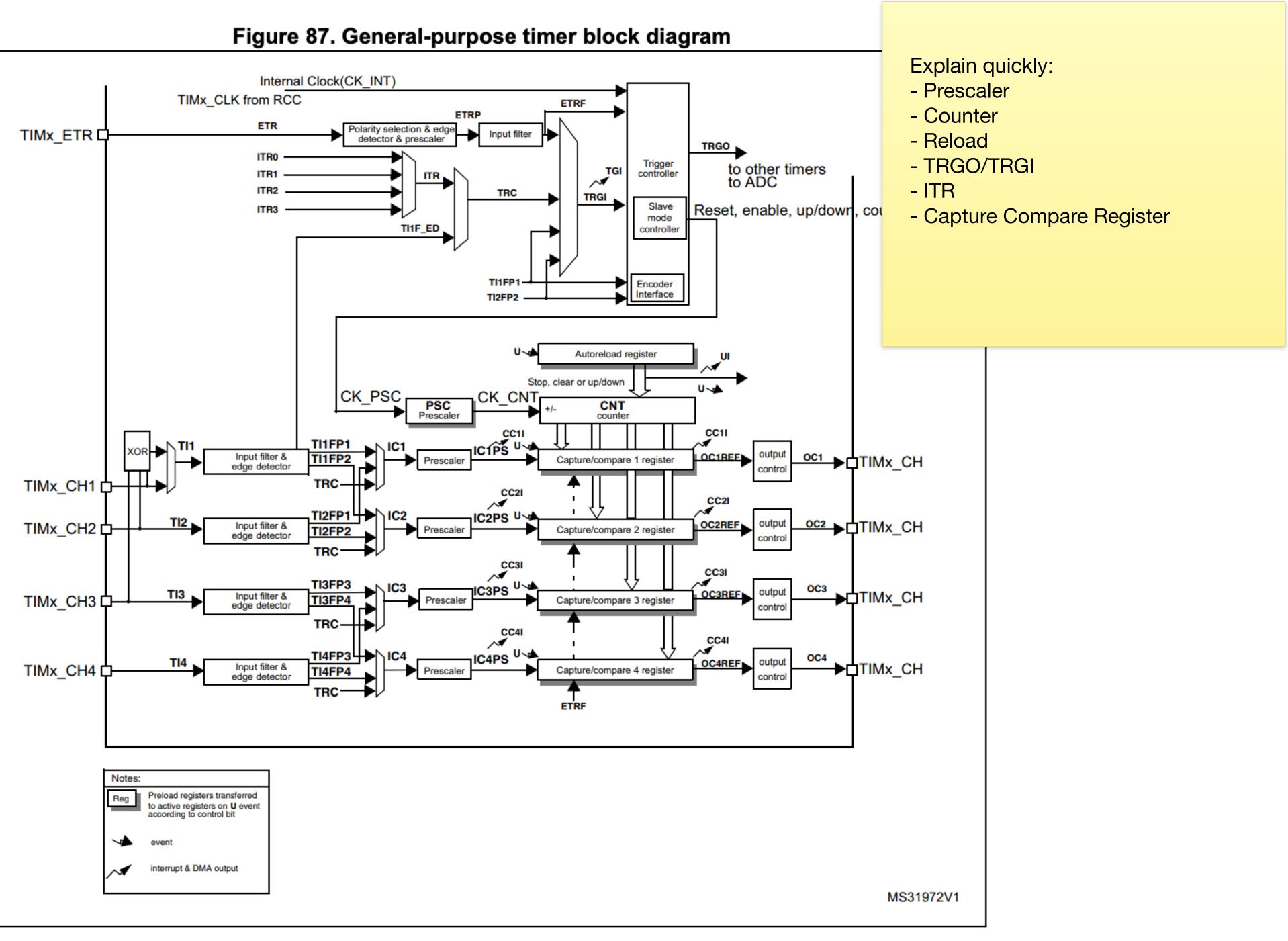

- STM32 DOCUMENTATION

- LEARNING TECHNIQUES

MIND MAPS

- ORGANISED LEARNING

- TIMERS/PWM

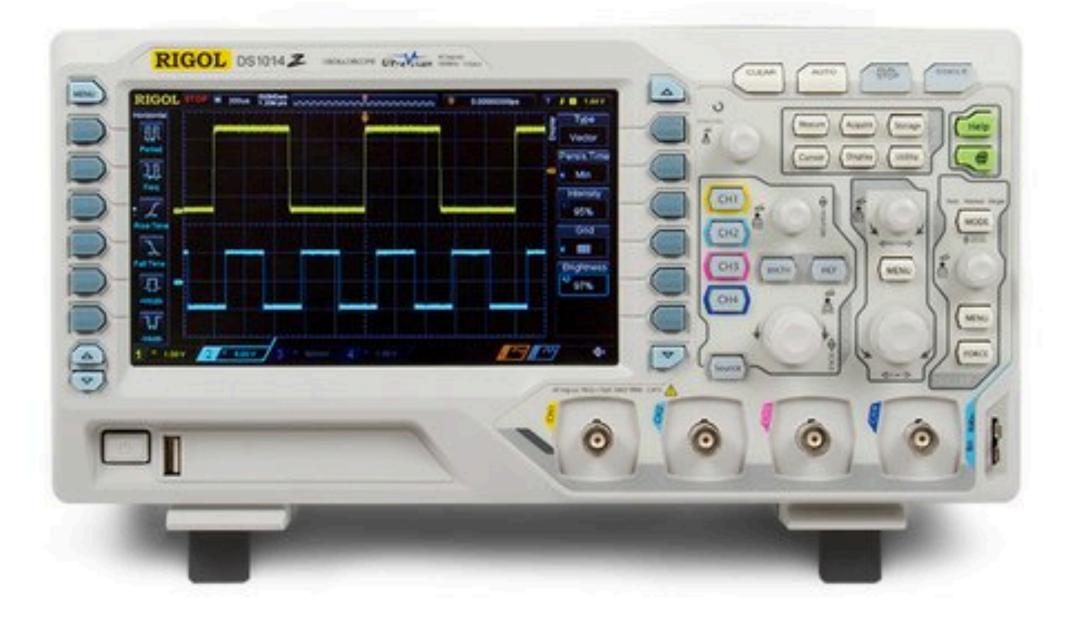

- DEBUGGING

- DMA/ADC

DEBUGGING

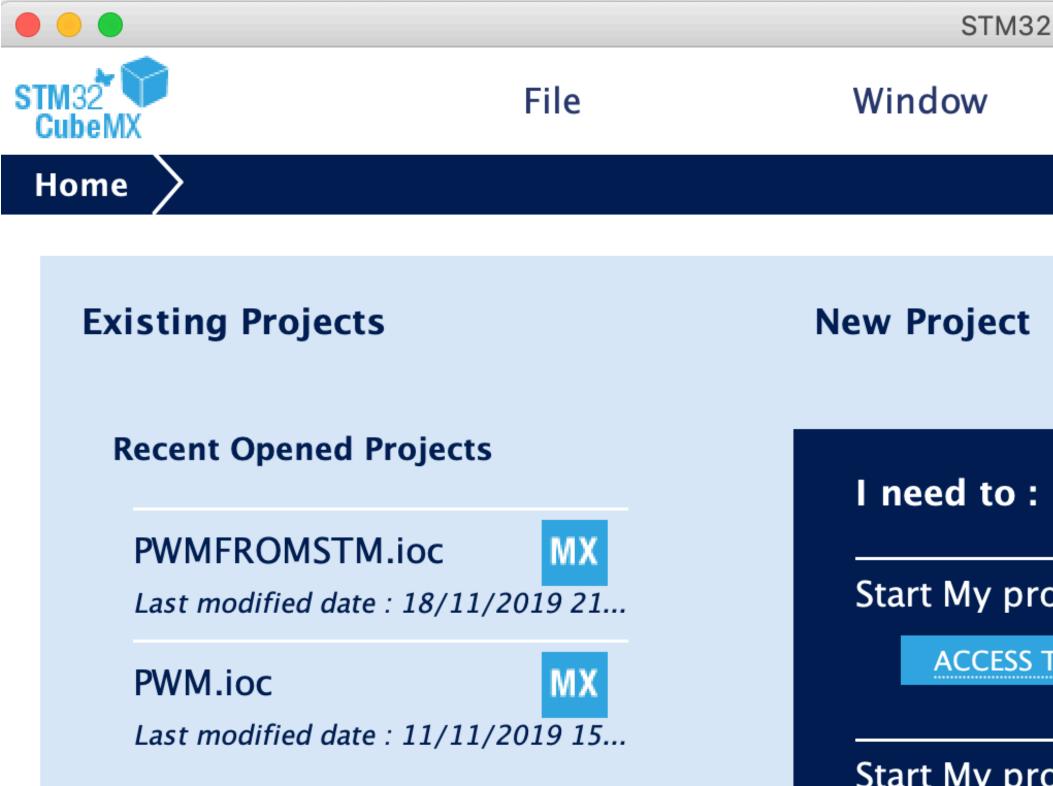

# **Preparing**<br/>Tools, documentation, organising.

**Other Projects**

#### STM32CubeMX Untitled

Help

#### Check for STM32CubeMX an...

CHECK FOR UPDATES

Install or remove embedded ...

INSTALL / REMOVE

Start My project from MCU

ACCESS TO MCU SELECTOR

Start My project from STBoard

ACCESS TO BOARD SELECTOR

Start My project from Cross ...

ACCESS TO CROSS SELECTOR

|                   | File                                                                                                         | ١                         | Window                   | Help                       | Q       | 🦻 🗗 🤇       |

|-------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|----------------------------|---------|-------------|

| Home > STM32F40   | 01RETx – NUCLE                                                                                               | EO-F401RE                 | > Untitled – Pro         | oject Manager $ ightarrow$ |         | GENERATE CO |

| Pinout & Config   | guration                                                                                                     | Clock Cont                | figuration               | Project                    | Manager |             |

| Project           | Project Settings –<br>Project Name<br>PWMFROMSTM<br>Project Location<br>/Users/psuwala,<br>Application Strue | /projects/STM32/<br>:ture |                          | Browse                     |         |             |

| Code Generator    | Basic<br>Toolchain Folder                                                                                    | ~                         | Do not generat           |                            |         |             |

| Advanced Settings | Linker Settings<br>Minimum Heap S<br>Minimum Stack S                                                         | ize 0x200                 | ake bas                  | ed IDE                     |         |             |

|                   | Mcu and Firmwar<br>Mcu Reference<br>STM32F401RETx<br>Firmware Packag<br>STM32Cube FW_                        | e Name and Versior        | n<br>] 🔽 Use latest avai | lable version              |         |             |

#### & Configuration

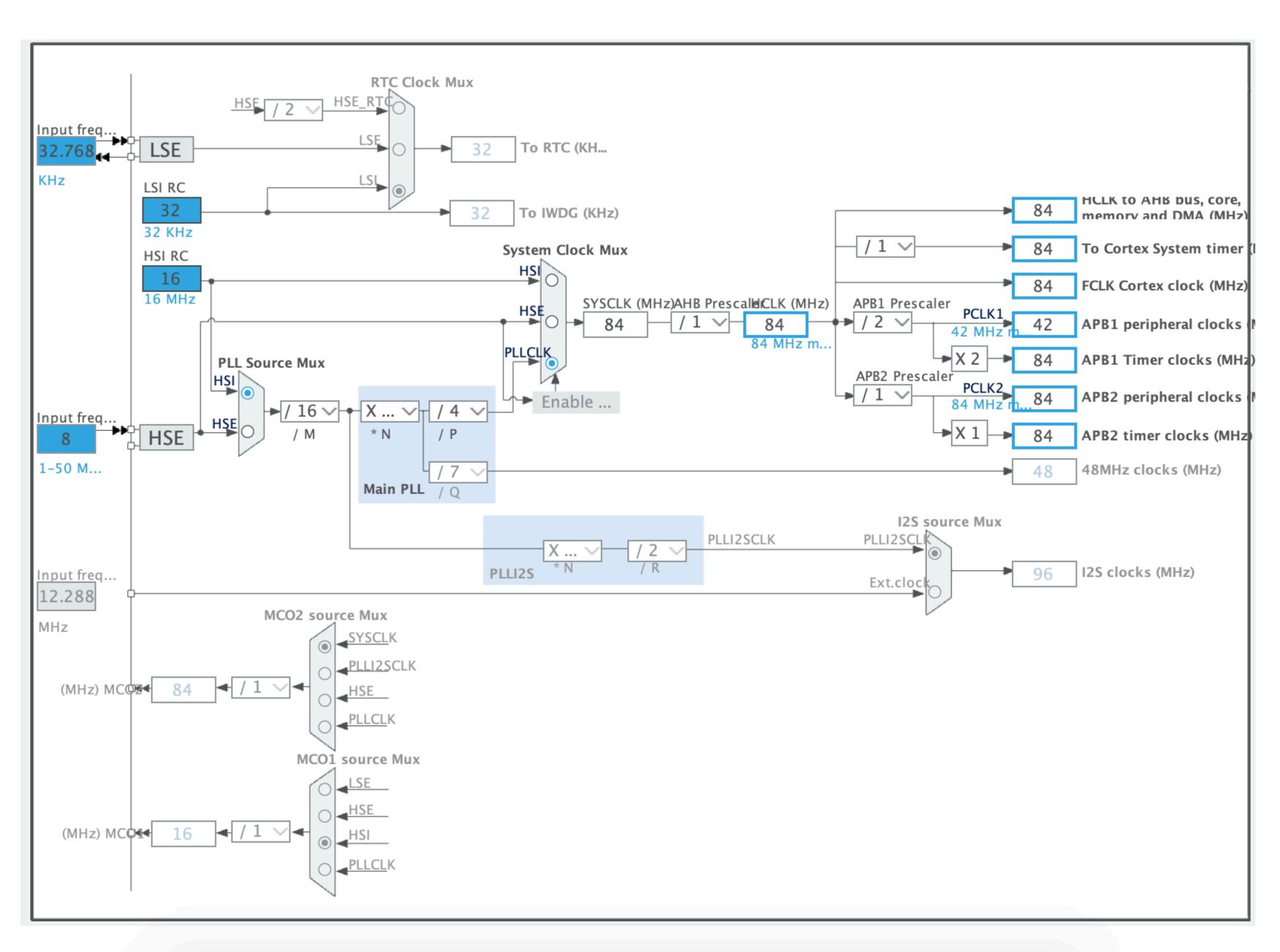

#### **Clock Configuration**

≏

$\stackrel{>}{\simeq}$

3

Tools

Resolve Clock Issues

Ð

23 Q

#### TIM2 Mode and Configuration

Mode

| Slave Mode Disable                 |        |  |  |  |  |  |  |  |

|------------------------------------|--------|--|--|--|--|--|--|--|

| Trigger Source Disable 🗸           |        |  |  |  |  |  |  |  |

| Clock Source Internal Clock        | $\sim$ |  |  |  |  |  |  |  |

| Channel1 PWM Generation CH1 $\sim$ |        |  |  |  |  |  |  |  |

| Channel2 Disable 🗸                 |        |  |  |  |  |  |  |  |

| Channel3 Disable 🗸                 |        |  |  |  |  |  |  |  |

| Channel4 Disable                   |        |  |  |  |  |  |  |  |

| Combined Channels Disable          |        |  |  |  |  |  |  |  |

|                                    |        |  |  |  |  |  |  |  |

#### Configuration

Reset Configuration

| 🥺 NVIC Settings                  | 😔 DMA            | A Settings     | 🥺 GPIO Settings            |  |  |  |  |  |  |

|----------------------------------|------------------|----------------|----------------------------|--|--|--|--|--|--|

| 😔 Parameter Set                  | tings            |                | 🥝 User Constants           |  |  |  |  |  |  |

| Configure the below parameters : |                  |                |                            |  |  |  |  |  |  |

| Q Search (CrtI+F)                | $\odot$          |                | 0                          |  |  |  |  |  |  |

| Counter Settings                 | Counter Settings |                |                            |  |  |  |  |  |  |

| Prescaler (PSC – 1               | 6 bits value)    | 8400           |                            |  |  |  |  |  |  |

| Counter Mode                     |                  | Up             |                            |  |  |  |  |  |  |

| Counter Period (A                | utoReload        | 10000          |                            |  |  |  |  |  |  |

| Internal Clock Div               | ision (CKD)      | No Division    |                            |  |  |  |  |  |  |

| auto-reload prelo                | ad               | Enable         |                            |  |  |  |  |  |  |

| ∨ Trigger Output (TRGO) Pa       | arameters        |                |                            |  |  |  |  |  |  |

| Master/Slave Mod                 | e (MSM bit)      | Disable (Trigg | ger input effect not delay |  |  |  |  |  |  |

| Trigger Event Sele               | ction            | Update Event   |                            |  |  |  |  |  |  |

| $\sim$ PWM Generation Channel    | 1                |                |                            |  |  |  |  |  |  |

| Mode                             |                  | PWM mode 1     |                            |  |  |  |  |  |  |

#### 🛄 Pinout view

#### System view

$\Theta$  []  $\Theta$   $\square$   $\square$   $\Box$

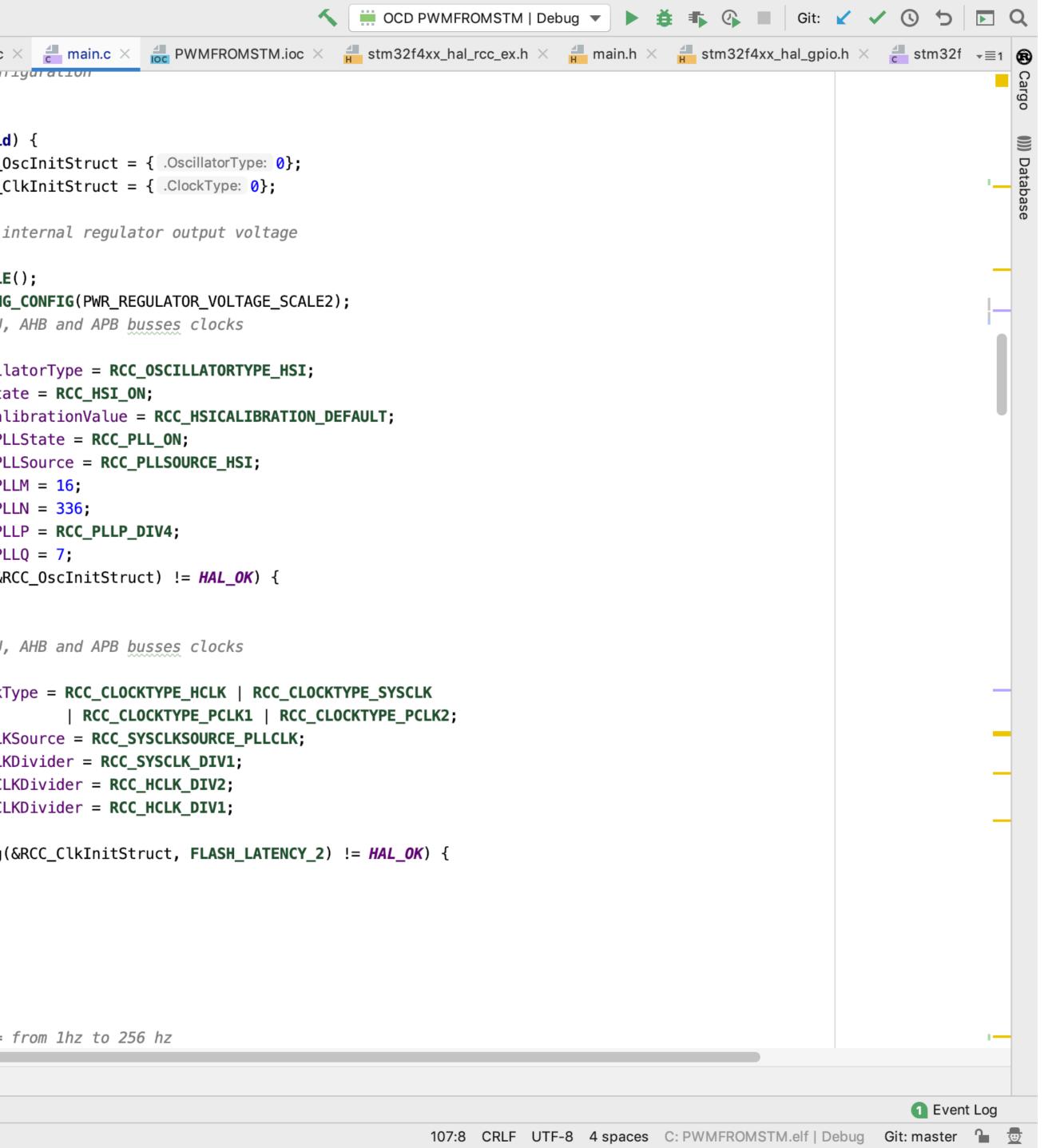

```

/**

* @brief System Clock Configuration

* @retval None

*/

void SystemClock_Config(void) {

RCC_0scInitTypeDef RCC_0scInitStruct = { .OscillatorType: 0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = { .ClockType: 0};

/** Configure the main internal regulator output voltage

*/

___HAL_RCC_PWR_CLK_ENABLE();

____HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE2);

/** Initializes the CPU, AHB and APB busses clocks

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI;

RCC_0scInitStruct.HSIState = RCC_HSI_ON;

RCC_OscInitStruct.HSICalibrationValue = RCC_HSICALIBRATION_DEFAULT;

RCC_0scInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_0scInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSI;

RCC_0scInitStruct.PLL.PLLM = 16;

RCC_0scInitStruct.PLL.PLLN = 336;

RCC_0scInitStruct.PLL.PLLP = RCC_PLLP_DIV4;

RCC_0scInitStruct.PLL.PLLQ = 7;

if (HAL_RCC_0scConfig(&RCC_0scInitStruct) != HAL_0K) {

Error_Handler();

/** Initializes the CPU, AHB and APB busses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK | RCC_CLOCKTYPE_SYSCLK

RCC_CLOCKTYPE_PCLK1 | RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2;

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2) != HAL_OK) {

Error_Handler();

}

```

| Project 🔻                      | $\odot$ | <b>▼</b> | <b>\$</b> - |            | /stem_s    | tm32f4xx.c 🛛 📥 stm32f4xx_it.c          |

|--------------------------------|---------|----------|-------------|------------|------------|----------------------------------------|

| PWMFROMSTM ~/projects/ST       | M32/P   | WMF      | ROMS        | 118        |            | * <u>@retval</u> None                  |

| 🕨 🖿 cmake-build-debug          |         |          |             | 119        |            | */                                     |

| CMakeFiles                     |         |          |             | 120        | <b>≒</b> ∎ | <pre>void SystemClock_Config(voi</pre> |

| Drivers                        |         |          |             | 121        | , Y        | RCC_OscInitTypeDef RCC_                |

|                                |         |          |             | 122        |            | RCC_ClkInitTypeDef RCC_                |

| STM32F4xx_HAL_Driver           |         |          |             | 123        |            |                                        |

|                                |         |          |             | 124        | Ģ          | /** Configure the main                 |

| main.h                         |         |          |             | 125        | 4          | */                                     |

|                                |         |          |             | 126        |            | HAL_RCC_PWR_CLK_ENABL                  |

| stm32f4xx_hal_conf.h           |         |          |             | 127        |            | HAL_PWR_VOLTAGESCALIN                  |

| stm32f4xx_it.h                 |         |          |             | 128        | Ģ          | <pre>/** Initializes the CPU</pre>     |

| Src                            |         |          |             | 129        | ф.         | */                                     |

| e main.c                       |         |          |             | 130        |            | RCC_0scInitStruct.0scil                |

| 🗧 stm32f4xx_hal_msp.c          |         |          |             | 131        |            | RCC_0scInitStruct.HSISt                |

| 📒 stm32f4xx_it.c               |         |          |             | 132        |            | RCC_OscInitStruct.HSICa                |

| syscalls.c                     |         |          |             | 133        |            | RCC_OscInitStruct.PLL.P                |

| 📒 system_stm32f4xx.c           |         |          |             | 134        |            | RCC_OscInitStruct.PLL.P                |

| startup                        |         |          |             | 135        |            | RCC_OscInitStruct.PLL.P                |

| startup_stm32f401xe.s          |         |          |             | 136        |            | RCC_OscInitStruct.PLL.P                |

| .cproject                      |         |          |             | 137        |            | RCC_OscInitStruct.PLL.P                |

| igdbinit                       |         |          |             | 138        |            | RCC_OscInitStruct.PLL.P                |

| gitignore                      |         |          |             | 139        |            | <pre>if (HAL_RCC_0scConfig(&amp;</pre> |

| <ul> <li>.mxproject</li> </ul> |         |          |             | 140        |            | l li loi_nanu ter (),                  |

|                                |         |          |             | 141        |            | /** Initializes the CPU                |

| osx.project                    |         |          |             | 143        | Ă          | */                                     |

| .project                       |         |          |             | 144        | T          | RCC_ClkInitStruct.Clock                |

| Cmake_install.cmake            |         |          |             | 145        |            |                                        |

| CMakeCache.txt                 |         |          |             | 146        |            | RCC_ClkInitStruct.SYSCL                |

| \Lambda CMakeLists.txt         |         |          |             | 147        |            |                                        |

| CMakeLists_template.txt        |         |          |             | 148        |            | RCC_ClkInitStruct.APB1C                |

| Makefile                       |         |          |             | 149        |            | RCC_ClkInitStruct.APB2C                |

| PWMFROMSTM.bin                 |         |          |             | 150        |            |                                        |

| 🗧 PWMFROMSTM.hex               |         |          |             | 151        |            | <pre>if (HAL_RCC_ClockConfig</pre>     |

| PWMFROMSTM.ioc                 |         |          |             | 152        |            | <pre>Error_Handler();</pre>            |

| PWMFROMSTM.map                 |         |          |             | 153        |            | }                                      |

| STM32F401RETx_FLASH.ld         |         |          |             | 154        | A3         | }                                      |

| External Libraries             |         |          |             | 155        | /          | //84MHZ / 8400 = 10khz                 |

| Scratches and Consoles         |         |          |             | 156        | #          | #define TIM2_PRESCALER 875             |

|                                |         |          |             | 157        | 4          | #define TIM2_RELOAD 8                  |

| Structure                      | \$      | <b>▼</b> | ф –         | 158        | Ξ.         |                                        |

| ↓: ↓ª ¥ 〒 丁                    |         |          |             | 159<br>160 |            | * OUR NEEDED SPEED RANGE =             |

|                                |         |          |             |            |            | f main                                 |

| ≣ <u>6</u> : TODO <u> </u>     | >_ Term |          |             | ake        |            |                                        |

GPI0\_InitStruct.Pin = GPI0\_PIN\_1; GPI0\_InitStruct.Mode = GPI0\_MODE\_ANALOG; GPI0\_InitStruct.Pull = GPI0\_NOPULL; GPI0\_InitStruct. HAL\_GPI0\_I F ゙ Alternate F 📔 Mode F 🦢 Pin F 📔 Pull F 📔 Speed /\* USER CODE B /\* USER CODE END 4 \*/

- uint32\_t

- uint32\_t

- uint32\_t

- uint32\_t

- uint32\_t

###

### Store

# How do I apply?

There are a few ways you can apply for a free license. The best way is to use your official institutional em address or ISIC card. In this case, it will only take you a few minutes to get a free educational license pac

You can also apply with a student/teacher card or any other official document certifying your affiliation your academic institution. Such applications may take several days to process.

Before applying, make sure to read the License Terms carefully.

JetBrai

| ins  | T | 00 | olk |

|------|---|----|-----|

|      |   |    |     |

|      |   |    |     |

|      |   |    |     |

|      |   |    |     |

|      |   |    |     |

| nail |   |    |     |

| ck.  |   |    |     |

| wit  | h |    |     |

|      |   |    |     |

|      |   |    |     |

```

Open On-Chip Debugger 0.10.0

Licensed under GNU GPL v2

[For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

[Info : auto-selecting first available session transport "hla_swd". To override use 'transport select <transport>'.

Info : The selected transport took over low-level target control. The results might differ compared to plain JTAG/SWD

adapter speed: 2000 kHz

adapter_nsrst_delay: 100

none separate

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

Info : clock speed 1800 kHz

Info : STLINK v2 JTAG v29 API v2 SWIM v18 VID 0x0483 PID 0x374B

Info : using stlink api v2

Info : Target voltage: 3.276467

Info : stm32f4x.cpu: hardware has 6 breakpoints, 4 watchpoints

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

adapter speed: 1800 kHz

target halted due to debug-request, current mode: Thread

xPSR: 0x01000000 pc: 0x08001970 msp: 0x20018000

Info : Unable to match requested speed 8000 kHz, using 4000 kHz

Info : Unable to match requested speed 8000 kHz, using 4000 kHz

adapter speed: 4000 kHz

Info : accepting 'gdb' connection on tcp/3333

Info : device id = 0 \times 10016433

Info : flash size = 512kbytes

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

adapter speed: 1800 kHz

target halted due to debug-request, current mode: Thread

xPSR: 0x01000000 pc: 0x08001970 msp: 0x20018000

Info : Unable to match requested speed 8000 kHz, using 4000 kHz

Info : Unable to match requested speed 8000 kHz, using 4000 kHz

adapter speed: 4000 kHz

target halted due to breakpoint, current mode: Thread

xPSR: 0x61000000 pc: 0x20000046 msp: 0x20018000

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

adapter speed: 1800 kHz

target halted due to debug-request, current mode: Thread

xPSR: 0x01000000 pc: 0x08001970 msp: 0x20018000

```

MacBook-Pro-Piotr :: projects/STM32/PWMFROMSTM (master\*) » sudo openocd -f interface/stlink-v2-1.cfg -f target/stm32f4x.cfg -c init -c "reset init"

[MacBook-Pro-Piotr :: projects/STM32/PWMFROMSTM <master\*> >> cat .gdbinit tar remote :3333 load PWMFROMSTM.elf file PWMFROMSTM.elf [MacBook-Pro-Piotr :: projects/STM32/PWMFROMSTM <master\*> >> arm-none-eabi-gdb GNU gdb (GNU Tools for Arm Embedded Processors 8-2018-q4-major) 8.2.50.20181213-git Copyright (C) 2018 Free Software Foundation, Inc. License GPLv3+: GNU GPL version 3 or later <http://gnu.org/licenses/gpl.html> This is free software: you are free to change and redistribute it. There is NO WARRANTY, to the extent permitted by law. Type "show copying" and "show warranty" for details. This GDB was configured as "--host=x86\_64-apple-darwin10 --target=arm-none-eabi". Type "show configuration" for configuration details. For bug reporting instructions, please see: <http://www.gnu.org/software/gdb/bugs/>. Find the GDB manual and other documentation resources online at: <http://www.gnu.org/software/gdb/documentation/>.

For help, type "help". Type "apropos word" to search for commands related to "word". warning: No executable has been specified and target does not support determining executable automatically. Try using the "file" command. 0x08001970 in ?? () Loading section .isr\_vector, size 0x194 lma 0x8000000 Loading section .text, size 0x18a0 lma 0x800194 Loading section .rodata, size 0x10 lma 0x8001a34 Loading section .init\_array, size 0x4 lma 0x8001a44 Loading section .fini\_array, size 0x4 lma 0x8001a50 Loading section .data, size 0xc lma 0x8001a54 Start address 0x8001970, load size 6752 Transfer rate: 11 KB/sec, 964 bytes/write. (gdb)

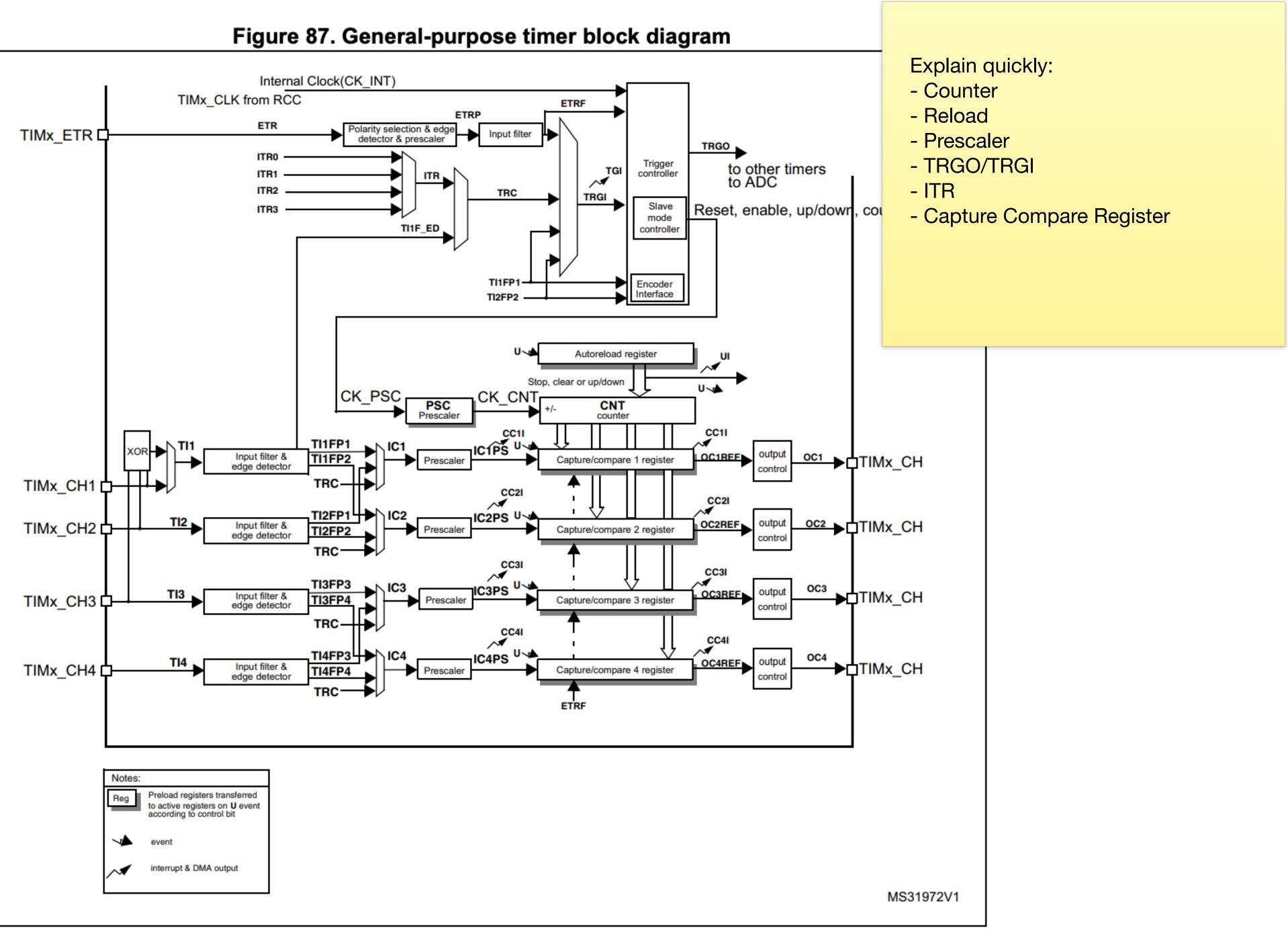

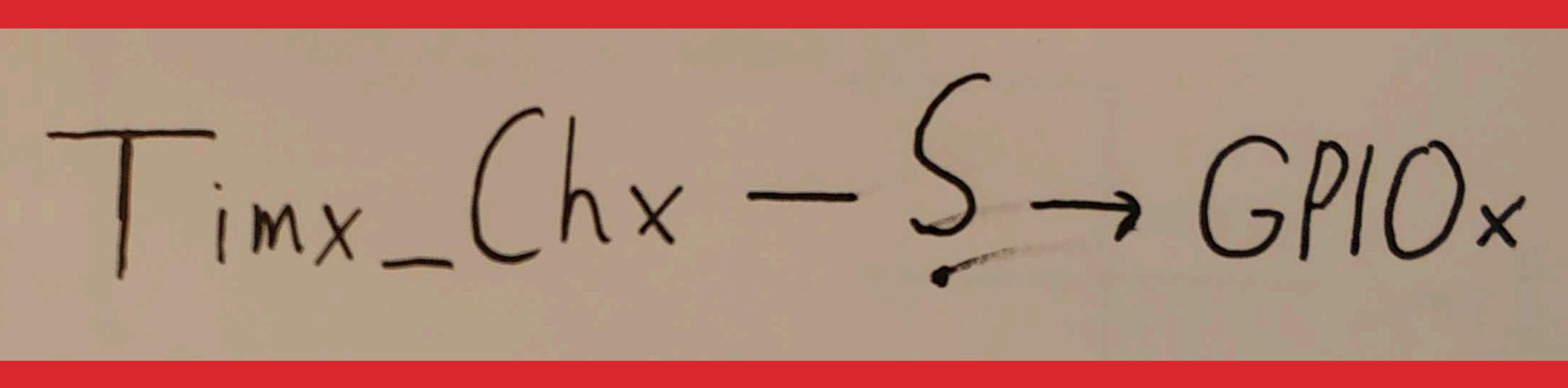

#### General-purpose timers (TIM2

- 13.1 TIM2 to TIM5 introduction .

- 13.2 TIM2 to TIM5 main features

- 13.3 TIM2 to TIM5 functional desc

- 13.3.1 Time-base unit . . . .

- 13.3.2 Counter modes . . .

- 13.3.3 Clock selection . . . .

- 13.3.4 Capture/compare cha

- 13.3.5 Input capture mode

- 13.3.6 PWM input mode . . .

- 13.3.7 Forced output mode .

- 13.3.8 Output compare mode

- 13.3.9 PWM mode . . . . . .

- 13.3.10 One-pulse mode ...

- 13.3.11 Clearing the OCxREF

- 13.3.12 Encoder interface mod

- 13.3.13 Timer input XOR func

- 13.3.14 Timers and external tr

- 13.3.15 Timer synchronization

- 13.3.16 Debug mode . . . . .

13

| to TIM5)                    |

|-----------------------------|

|                             |

|                             |

| cription                    |

|                             |

|                             |

|                             |

| nnels                       |

|                             |

|                             |

|                             |

| ə                           |

|                             |

|                             |

| signal on an external event |

| de                          |

| tion                        |

| rigger synchronization      |

| 1                           |

|                             |

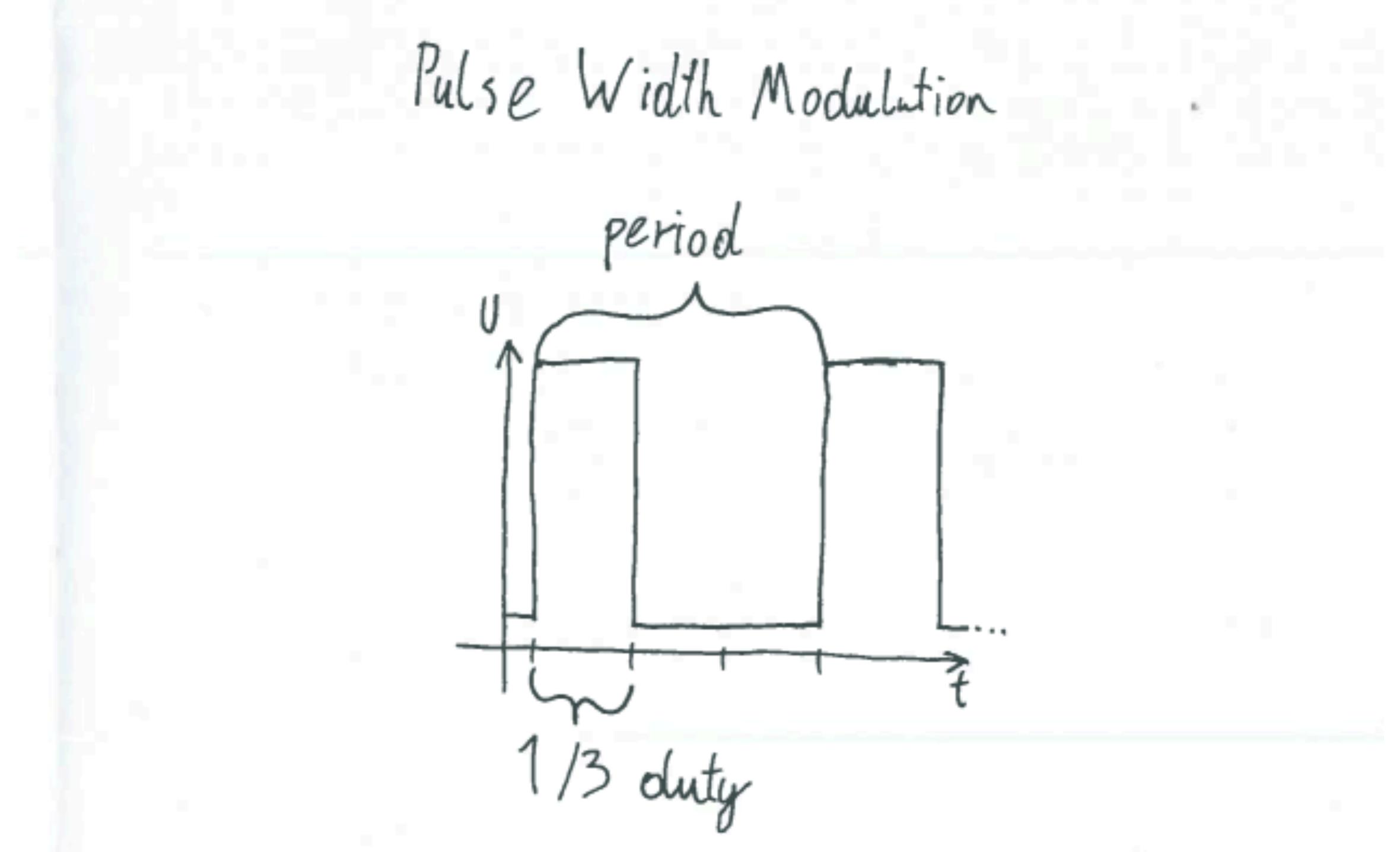

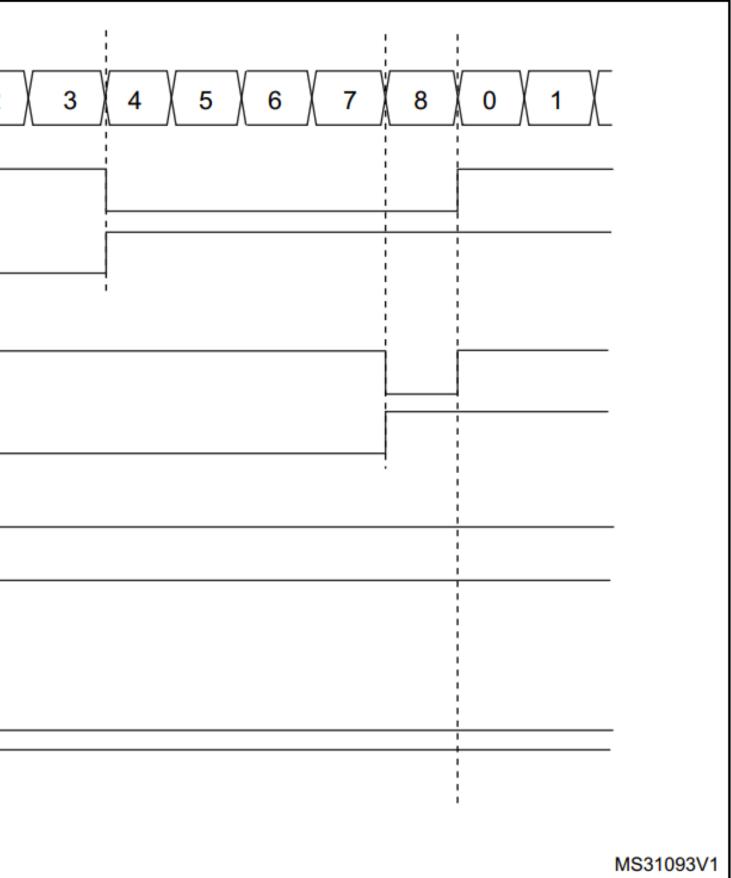

#### PWM edge-aligned mode

#### Upcounting configuration

Upcounting is active when the DIR bit in the TIMx\_CR1 register is low. Refer to Upcounting mode.

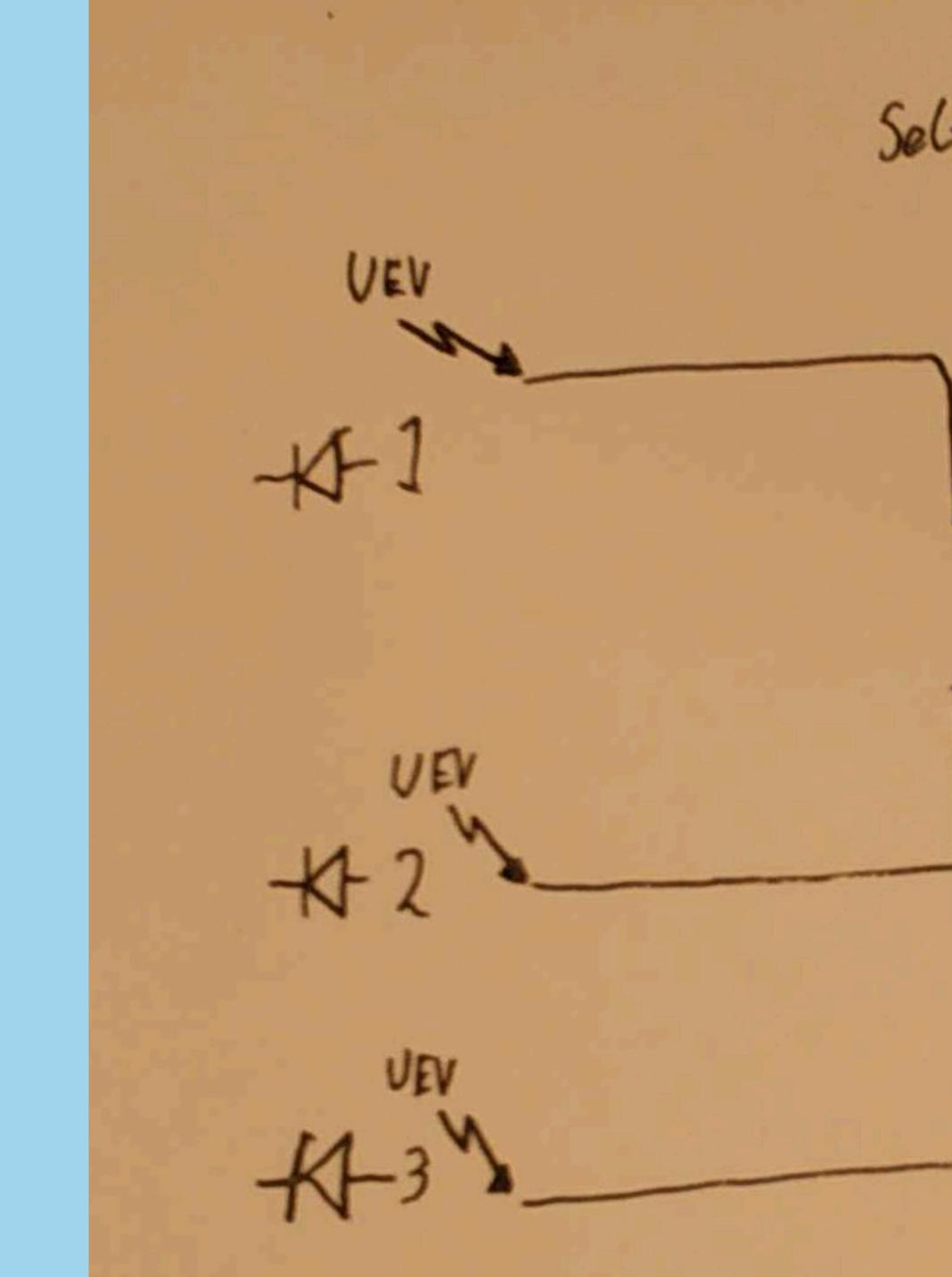

In the following example, we consider PWM mode 1. The reference PWM signal OCxREF is high as long as TIMx\_CNT <TIMx\_CCRx else it becomes low. If the compare value in TIMx\_CCRx is greater than the auto-reload value (in TIMx\_ARR) then OCxREF is held at '1. If the compare value is 0 then OCxREF is held at '0. *Figure 117* shows some edge-aligned PWM waveforms in an example where TIMx\_ARR=8.

#### Counter register 2 OCXREF CCRx=4 CCxIF OCXREF CCRx=8 CCxIF OCXREF '1' CCRx>8 CCxIF OCXREF **'0'** CCRx=0 **CCxIF**

#### Figure 117. Edge-aligned PWM waveforms (ARR=8)

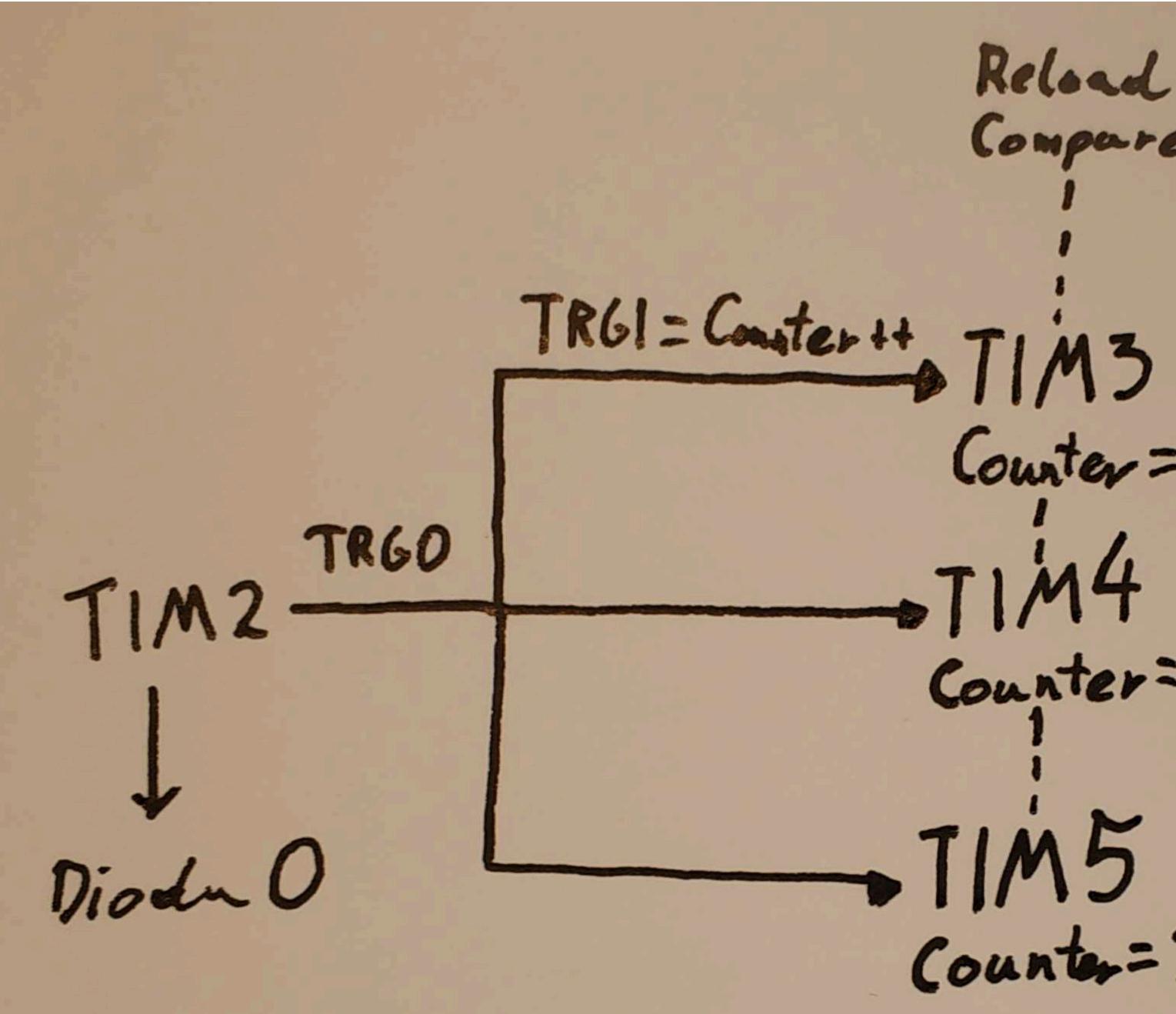

Reload = 2 Compare =0 Compare Counter Dioda 1 Counter = 0 TIM4 Counter=1 Dioda2 TIM5 Counter=2

### 13.4 TIM2 to TIM5 registers . . . .

- 13.4.1 TIMx control register 1

- 13.4.2 TIMx control register 2

- 13.4.3 TIMx slave mode control

- 13.4.4 TIMx DMA/Interrupt ena

- 13.4.5 TIMx status register (T

- 13.4.6 TIMx event generation

- 13.4.7 TIMx capture/compare

- 13.4.8 TIMx capture/compare

- 13.4.9 TIMx capture/compare

- 13.4.10 TIMx counter (TIMx\_CN

- 13.4.11 TIMx prescaler (TIMx\_I

- 13.4.12 TIMx auto-reload regist

- 13.4.13 TIMx capture/compare

- 13.4.14 TIMx capture/compare

| (TIMx_CR1)                   |

|------------------------------|

| (TIMx_CR2)                   |

| ol register (TIMx_SMCR)      |

| able register (TIMx_DIER)    |

| IMx_SR)                      |

| register (TIMx_EGR)          |

| mode register 1 (TIMx_CCMR1) |

| mode register 2 (TIMx_CCMR2) |

| enable register (TIMx_CCER)  |

| NT)                          |

| PSC)                         |

| ter (TIMx_ARR)               |

| register 1 (TIMx_CCR1)       |

| register 2 (TIMx_CCR2)       |

#### 13.4.1 TIMx control register 1 (TIMx\_CR1)

Address offset: 0x00

Reset value: 0x0000

13 12 11 10 15 14 Reserved

| Bits 15:10 | Reserved, must be kept                                                                                                                                                                                                                                                                              |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits 9:8   | <b>CKD</b> : Clock division<br>This bit-field indicates<br>sampling clock used b<br>00: $t_{DTS} = t_{CK\_INT}$<br>01: $t_{DTS} = 2 \times t_{CK\_INT}$<br>10: $t_{DTS} = 4 \times t_{CK\_INT}$<br>11: Reserved                                                                                     |

| Bit 7      | ARPE: Auto-reload preid<br>0: TIMx_ARR register<br>1: TIMx_ARR register                                                                                                                                                                                                                             |

| Bits 6:5   | CMS: Center-aligned mod<br>00: Edge-aligned mod<br>(DIR).<br>01: Center-aligned mod<br>interrupt flags of chan<br>only when the counter<br>10: Center-aligned mod<br>interrupt flags of chan<br>only when the counter<br>11: Center-aligned mod<br>interrupt flags of chan<br>both when the counter |

| Bit 4      | DIR: Direction<br>0: Counter used as up<br>1: Counter used as do<br>Note: This bit is read of<br>mode.                                                                                                                                                                                              |

| Bit 3      | <b>OPM</b> : One-pulse mode<br>0: Counter is not stopp<br>1: Counter stops counter                                                                                                                                                                                                                  |

| 9        | 8  | 7    | 6 5 |    | 4   | 3   | 2   | 1    | 0   |

|----------|----|------|-----|----|-----|-----|-----|------|-----|

| CKD[1:0] |    | ARPE | CMS |    | DIR | OPM | URS | UDIS | CEN |

| rw       | rw | rw   | rw  | rw | rw  | rw  | rw  | rw   | rw  |

ept at reset value.

es the division ratio between the timer clock (CK\_INT) frequency and by the digital filters (ETR, Tlx),

NΤ NT

reload enable

ter is not buffered

ter is buffered

mode selection

ode. The counter counts up or down depending on the direction bit

mode 1. The counter counts up and down alternatively. Output compare annels configured in output (CCxS=00 in TIMx\_CCMRx register) are set ter is counting down.

mode 2. The counter counts up and down alternatively. Output compare annels configured in output (CCxS=00 in TIMx\_CCMRx register) are set ter is counting up.

mode 3. The counter counts up and down alternatively. Output compare annels configured in output (CCxS=00 in TIMx\_CCMRx register) are set ter is counting up or down.

d to switch from edge-aligned mode to center-aligned mode as long as enabled (CEN=1)

upcounter

downcounter

only when the timer is configured in Center-aligned mode or Encoder

opped at update event

unting at the next update event (clearing the bit CEN)

More important things I marked with colours so I could connect with each other.

10 19 nation of the state

\*/8/.10/27

the function in GPIO<sub>X</sub> ODR

38/13

**B**<sub>1</sub>

6

let, each Ware in

A

HACKER: SPACE Ports : WARMETATY I ZABAWA I SPOLECZNOSC TIM 2= PAD CH1 Update = yougs what is update Ended IM 3 = PBO CH3 Dirr TIM4 = PB7 CH2 Update Regart Gource the mass CMS TIM 5= PA1 CH2 Conta 0+2 Reload + 724 - Vulse + 0x24 One Palse Mode OFF Auto Adond Preland ? FREQ - TIM2 - ENABLE CR1 = 0000 00 00 10010101 FCK-PSC/ APB1 Update ASTR60 = Reloads TIMMESCALER + + Ox28 TII SEL DMA ENABLE CLOCK TRCO Reserved Rescred PWM f0x04 0000 0000 0 0100000 -CRZ CC1 not affected CCR1 Confort by ETR1 putered first constant discussed C (MR7=+0,18 Ox32 + Congre Value 326:4 (compre) Output - PUAI (Clis ((2 0000 00000110 7000 Pileritz Butter High 1 VARIABLES Time 0x20 Other Chunnels (CER - 0000 0000 0000 0001 APB1 CLK TIMER = 8+MHZ Output TIMZ PRESCALER= 8+00-1 TIME FREQ Compre Value = 5k 5 2 15 GPIO 97 NOT INCLUDED7 - - -

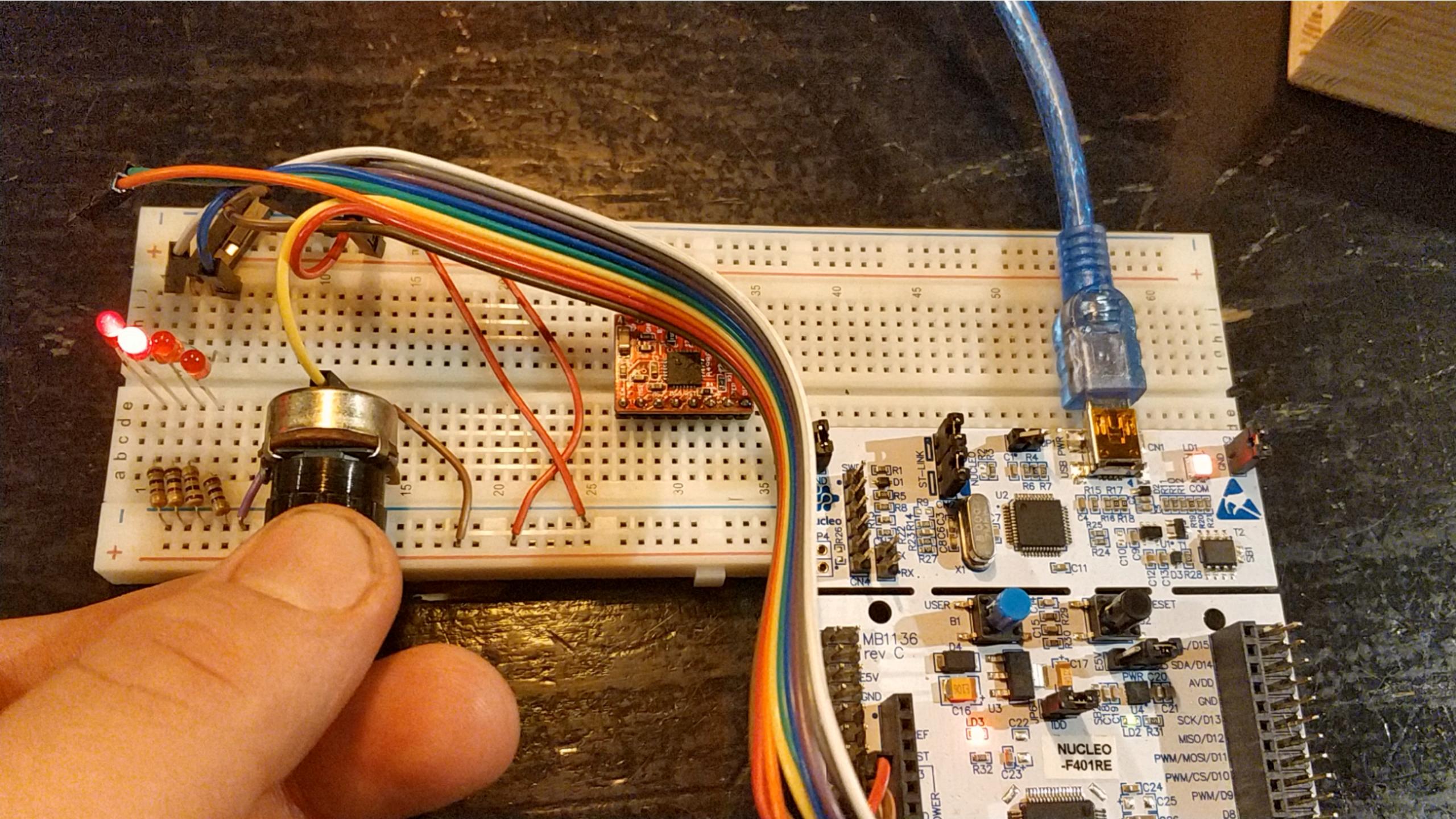

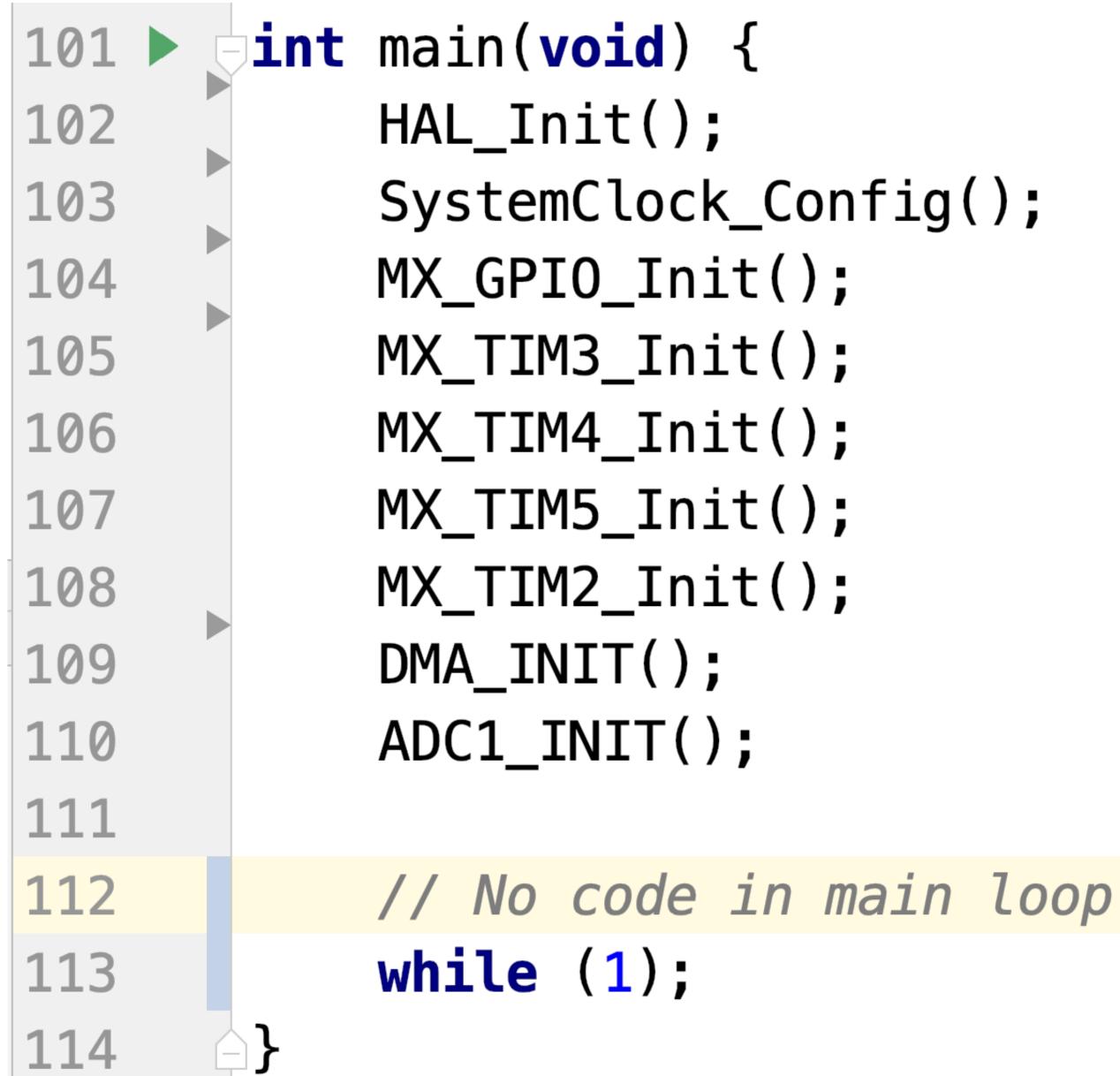

# **Execution of plan** Code & Debugging

]/\*\*

```

* Obrief TIM2 Initialization Function

```

```

* <u>@param</u> None

```

```

* @retval None

```

) \*/

```

static void MX_TIM2_Init(void) {

```

//START WITH THE COCK!?

void \*TIM2\_ADDR = (0x40000000);

uint16\_t  $*TIM2_ENABLE = ((uint16_t * )(TIM2_ADDR + 0x00));$ uint16\_t  $*TIM2\_ENABLE_2 = ((uint16_t * )(TIM2\_ADDR + 0x04));$ uint16\_t  $*TIM2_COMPARE_MODE = ((uint16_t * )(TIM2_ADDR + 0x18));$ uint16\_t \*TIM2\_COMPARE\_OUTPUT\_MODE = ((uint16\_t \* )(TIM2\_ADDR + 0x20)); uint32\_t  $*TIM2_COUNTER_VALUE = ((uint32_t * )(TIM2_ADDR + 0x24));$ uint16\_t \*TIM2\_PRESCALER\_VALUE = ((uint16\_t \* )(TIM2\_ADDR + 0x28)); uint32\_t \*TIM2\_RELOAD\_VALUE = ((uint32\_t \* )(TIM2\_ADDR + 0x2C)); uint32\_t  $*TIM2_COMPARE_VALUE = ((uint32_t * )(TIM2_ADDR + 0x34));$

#### \_\_\_HAL\_RCC\_TIM2\_CLK\_ENABLE(); important

\*TIM2\_ENABLE = 0b0000000000000010010001; // autoreload + counter enabled - at the end as I am scared

$*TIM2_PRESCALER_VALUE = 8400 - 1;$  //down to 10khz \*TIM2\_RELOAD\_VALUE = 10000; //down to 1hz for PWM \*TIM2\_COUNTER\_VALUE = \*TIM2\_RELOAD\_VALUE; //as we have downcounting

\*TIM2\_COMPARE\_VALUE = 5000; //half of it \*TIM2\_COMPARE\_MODE = 0b00000000001101000; // PWM1 MODE of compare + preload enabled (!?) \*TIM2\_COMPARE\_OUTPUT\_MODE = 0b000000000000001; // ENABLE OUTPUT

1}

\*TIM2\_ENABLE\_2 = 0b0000000000000000; // Update = reload as external trigger //FOR LATER - change it to channel then

3/\*\*

\* **@brief** TIM2 Initialization Function

\* <u>@param</u> None

\* @retval None

```

) */

```

# static void MX\_TIM2\_Init(void) { \_\_\_HAL\_RCC\_TIM2\_CLK\_ENABLE();

TIMx\_Init(

timerAddr: (void \*) 0x4000000, compareValueAddrOffset: 0x34, compareModeAddrOffset: 0x18, enable: TIMx\_ENABLE, // autoreload + counter enabled enable2: 0b010u << 4u, // Using update as external trigger slaveMode: 0b0, // I'm master, not slave TIM2\_PRESCALER, // PRESCALING AS A PART TIM2\_RELOAD, // THIS VALUE WILL BE TAKEN FROM ADC SOON TIM2\_RELOAD, // IT COULD BE EVEN 0, it doesn't matter compareValue: TIM2\_RELOAD / 2, // half on, half dead compareMode: 0b110u << 4u | 0b1u << 3u, // PWM1 MODE of compare + preload enabled (!?) outputMode: 0b1); // Enable output for ch1

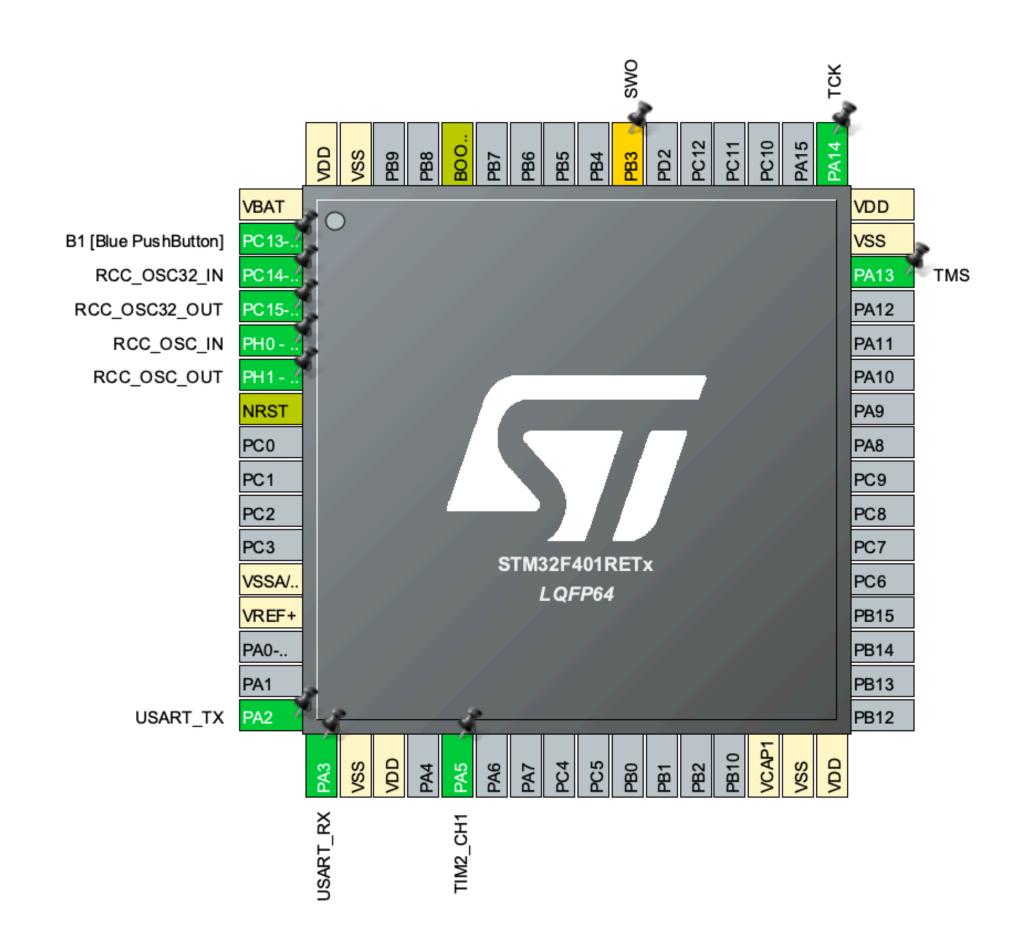

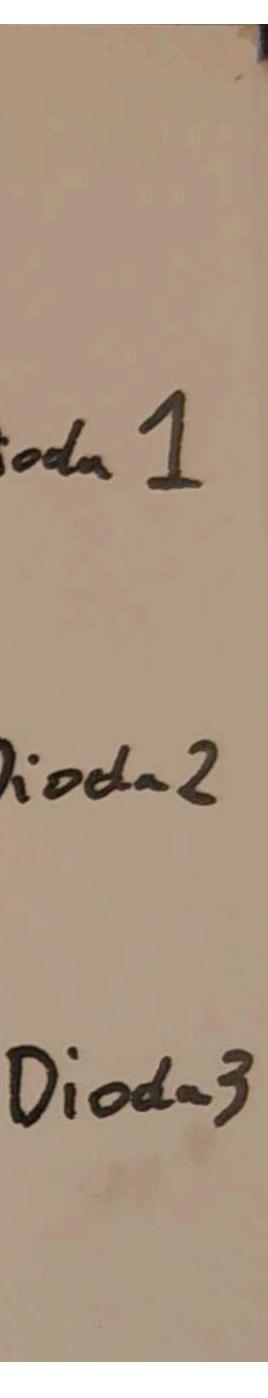

### **PROBLEM #1 - WHICH CHANNEL IS WHICH AF?**

# REPETITION

#### Pinouts and pin description

|        | Table 8. STM32F401xD/xE pin definitions (continued) |        |         |          |                                                      |                                                         |    |       |                                                         |                         |  |

|--------|-----------------------------------------------------|--------|---------|----------|------------------------------------------------------|---------------------------------------------------------|----|-------|---------------------------------------------------------|-------------------------|--|

|        | Pin                                                 | Nun    | nber    |          |                                                      | unction $\frac{1}{2}$ $\frac{1}{2}$ $\frac{1}{2}$ Alter |    |       |                                                         |                         |  |

| UQFN48 | WLCSP49                                             | LQFP64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after reset) <sup>(1)</sup> |                                                         |    | Notes | Alternate functions                                     | Additional<br>functions |  |

| 13     | E4                                                  | 17     | 26      | L3       | PA3                                                  | I/O                                                     | FT | -     | USART2_RX, TIM2_CH4,<br>TIM5_CH4, TIM9_CH2,<br>EVENTOUT | ADC1_IN3                |  |

| -      | -                                                   | 18     | 27      | -        | VSS                                                  | S                                                       | -  | -     | -                                                       | -                       |  |

| -      | -                                                   | 19     | 28      | -        | VDD                                                  | S                                                       | -  | -     | -                                                       | -                       |  |

| -      | -                                                   | -      | -       | E3       | BYPASS_<br>REG                                       | I                                                       | FT | -     | -                                                       | -                       |  |

| 14     | G6                                                  | 20     | 29      | М3       | PA4                                                  | I/O                                                     | FT | -     | SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK, EVENTOUT   | ADC1_IN4                |  |

| 15     | F5                                                  | 21     | 30      | K4       | PA5                                                  | I/O                                                     | FT | -     | SPI1_SCK,<br>TIM2_CH1/TIM2_ETR,<br>EVENTOUT             | ADC1_IN5                |  |

| 16     | F4                                                  | 22     | 31      | L4       | PA6                                                  | I/O                                                     | FT | -     | SPI1_MISO, TIM1_BKIN,<br>TIM3_CH1, EVENTOUT             | ADC1_IN6                |  |

| 17     | F3                                                  | 23     | 32      | M4       | PA7                                                  | I/O                                                     | FT | -     | SPI1_MOSI, TIM1_CH1N,<br>TIM3_CH2, EVENTOUT             | ADC1_IN7                |  |

| -      | -                                                   | 24     | 33      | K5       | PC4                                                  | I/O                                                     | FT | -     | EVENTOUT                                                | ADC1_IN14               |  |

| -      | -                                                   | 25     | 34      | L5       | PC5                                                  | I/O                                                     | FT | -     | EVENTOUT                                                | ADC1_IN15               |  |

| 18     | G5                                                  | 26     | 35      | M5       | PB0                                                  | I/O                                                     | FT | -     | TIM1_CH2N, TIM3_CH3,<br>EVENTOUT                        | ADC1_IN8                |  |

| 19     | G4                                                  | 27     | 36      | M6       | PB1                                                  | I/O                                                     | FT | -     | TIM1_CH3N, TIM3_CH4,<br>EVENTOUT                        | ADC1_IN9                |  |

#### STM32F401xD STM32F401xE

#### 9 STM22E404xD/xE nin definitions (contin -1\

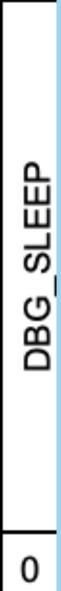

### **PROBLEM #2 - DIODES WERE DESYNCHRONISED**

Should Be - 0 - 0 0

Was 00 0

change of x in time status register configuration debuggable registers Symptoms Chiny correctly

reflects predicted states

(gdb) print /t \*((uint16\_t\*) 0x400000000) \$20 = 10001(gdb) print /t \*((uint16\_t\*) 0x40000004) \$21 = 100000(gdb) print /t \*((uint16\_t\*) 0x40000008) \$22 = O (gdb) print /t \*((uint16\_t\*) 0x4000000014) warning: value truncated \$23 = 1100011011001

Tim2 configuration registers.

Checked configured registers

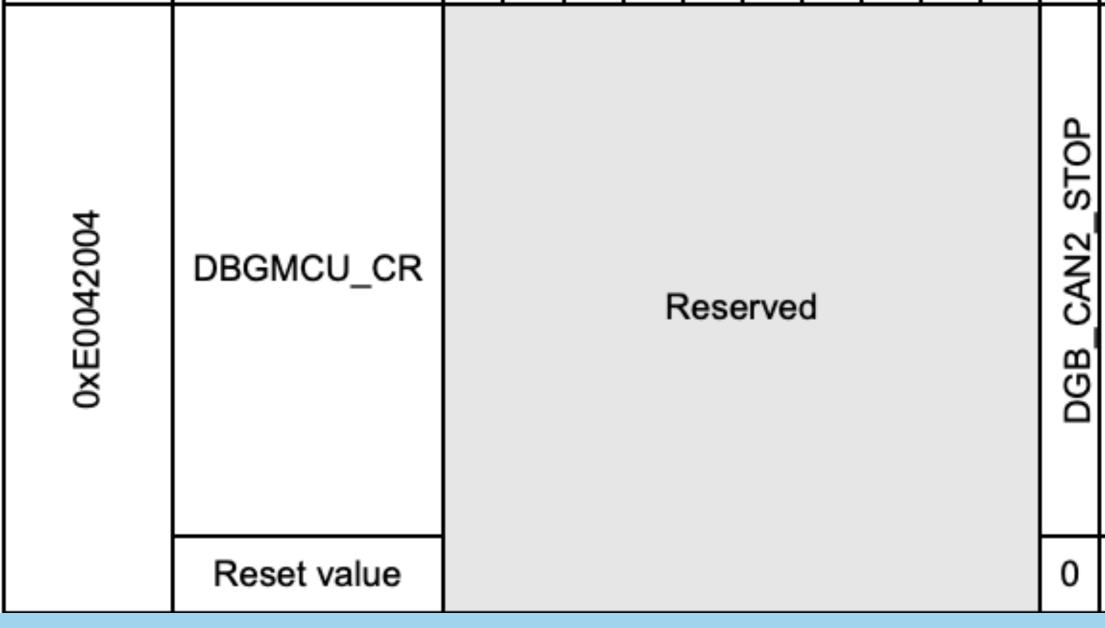

#### \*((uint32\_t \*) 0xE0042008) |= 0b1111u; // TIM2-5 STOP

| DBG_TIM7_STOP | DBG_TIM6_STOP | DBG_TIM5_STOP | DBG_TIM8_STOP | DBG_I2C2_SMBUS_TIMEOUT |   |   | DBG_TIM4 | DBG_TIM3_STOP | DBG_TIM2 | DBG_TIM1_STOP | DBG_WWDG_STOP | DBG_IWDGSTOP |   |   | TRACE_IOEN | Reserved | DBG_STANDBY | DBG_STOP |

|---------------|---------------|---------------|---------------|------------------------|---|---|----------|---------------|----------|---------------|---------------|--------------|---|---|------------|----------|-------------|----------|

| 0             | 0             | 0             | 0             | 0                      | 0 | 0 | 0        | 0             | 0        | 0             | 0             | 0            | 0 | 0 | 0          |          | 0           | 0        |

```

(gdb) l

//MX_USART2_UART_Init();

134

/* USER CODE BEGIN 2 */

135

136

137

/* USER CODE END 2 */

138

139

/* Infinite loop */

/* USER CODE BEGIN WHILE */

140

141

while (1) {

142

/* USER CODE END WHILE */

143

(gdb) l

/* USER CODE BEGIN 3 */

144

145

}

146

/* USER CODE END 3 */

}

147

148

149

/**

150

* @brief System Clock Configuration

151

* @retval None

152

*/

153

void SystemClock_Config(void) {

(gdb) b 141

(gdb) c

Continuing.

Note: automatically using hardware breakpoints for read-only addresses.

Breakpoint 1, main () at /Users/psuwala/projects/STM32/PWMFROMSTM/Src/main.c:141

141

while (1) {

(gdb) ^CQuit

(gdb) c

Continuing.

Breakpoint 1, main () at /Users/psuwala/projects/STM32/PWMFROMSTM/Src/main.c:141

141

while (1) {

(gdb) c

Continuing.

Breakpoint 1, main () at /Users/psuwala/projects/STM32/PWMFROMSTM/Src/main.c:141

while (1) {

141

(gdb) c

Continuing.

Breakpoint 1, main () at /Users/psuwala/projects/STM32/PWMFROMSTM/Src/main.c:141

while (1) {

141

(gdb) c

Continuing.

Breakpoint 1, main () at /Users/psuwala/projects/STM32/PWMFROMSTM/Src/main.c:141

while (1) {

141

(gdb) c

Continuing.

Breakpoint 1, main () at /Users/psuwala/projects/STM32/PWMFROMSTM/Src/main.c:141

while (1) {

141

(gdb) c

```

Breakpoint 1 at 0x80012b4: file /Users/psuwala/projects/STM32/PWMFROMSTM/Src/main.c, line 141.

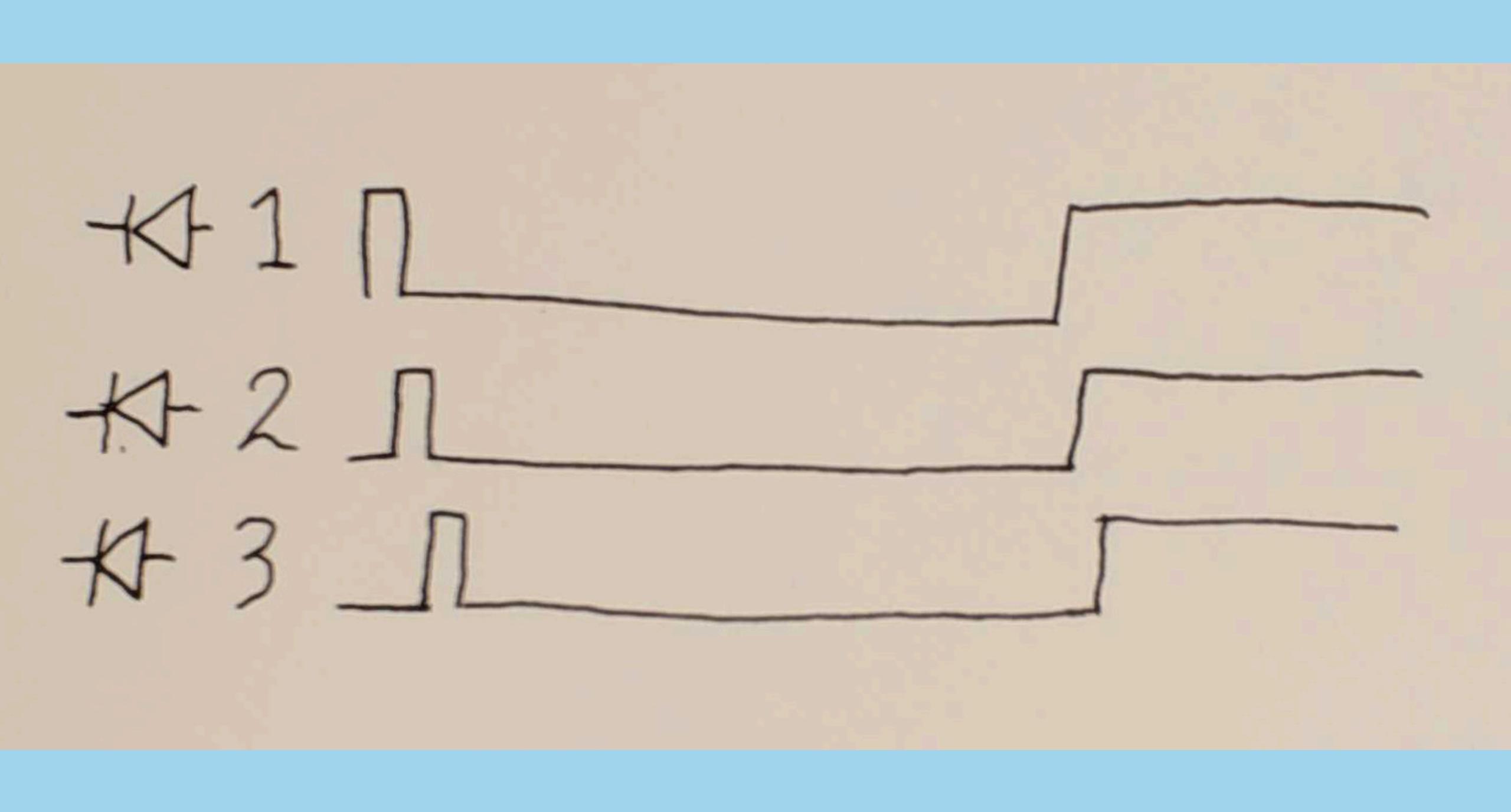

UIV = Updite Event KF1 DNUEV K-2 DNUEV AF 3 MAUEV UEV = shadou , actual registers registers shudow actual presculer > presculer

Solf Induced UEV

I had to execute update before I started timers.

#### \*TIM2\_UPDATE |= 1u; //whatever, lets just update

It was just updating one bit for every timer.

| 🔍 Altera MA               | ХІІ - ТорЈ               | TAG Probe        |                            |              |    |           |                  |                         |

|---------------------------|--------------------------|------------------|----------------------------|--------------|----|-----------|------------------|-------------------------|

| <u>F</u> ile <u>V</u> iew | <u>S</u> can <u>P</u> ir | ns <u>W</u> atch | W <u>a</u> veform <u>H</u> | <u>l</u> elp |    |           |                  |                         |

| / 👌 🗎                     | 🖸 Pins                   | ↔ Watch          | 🖄 Waveform                 | 100          | •  | 🕨 Run     | 🔄 JTAG Reset     | Tinstruction            |

| Pins                      |                          |                  |                            |              | ×  |           |                  | 410705056               |

| 1. CPLD : EPI             | M1270F256                |                  |                            |              | -  |           | CPLD : EPI       | 11270F256               |

| Name 🔻                    | Pin #                    | Port             | I/O Value                  | Туре         |    |           |                  |                         |

| we                        | P11                      | IOP11            | 1/1                        | inout 🔺      |    |           |                  |                         |

| oe                        | P12                      | IOP12            | 1/1                        | inout        |    |           |                  |                         |

| data[7:0]                 |                          |                  | 10/10 (hex)                | inout        |    |           |                  |                         |

| - <7>                     | P10                      | IOP10            | 0/0                        | inout        |    |           |                  |                         |

| - <6>                     | P9                       | IOP9             | 0/0                        | inout        |    |           |                  |                         |

| - <5>                     | P8                       | IOP8             | 0/0                        | inout        |    |           |                  |                         |

| - <4>                     | P7                       | TOP7             | 1/1                        | inout        | -  |           |                  |                         |

| Search pins               |                          |                  |                            | Ş            |    |           | EXT              | EST                     |

| Waveform                  |                          |                  |                            |              |    |           |                  |                         |

| 🏷   🗕 🛛                   | .5 min                   | ት 🕶 🛛 🕻          | \$ 🖨 🗭 👘                   |              |    |           |                  |                         |

| Name                      | Pin #                    | Туре             | 20                         |              | 40 | т. т.     | 6 <u>0</u> · · · | • <mark>80</mark> • • • |

| we                        | P11                      | out of           | inout                      |              |    |           |                  |                         |

| address[1]                | 7:0]                     | out of           | inout 15555                | 24444        | (1 | 5555      |                  | 24444                   |

| 🗏 data[7:0]               |                          | in of ir         |                            | 55           |    | (8        | 0 (AA            | 55                      |

| - <7>                     | P10                      | in of ir         |                            |              |    |           |                  |                         |

|                           |                          |                  | •                          |              |    | IN of inc |                  |                         |

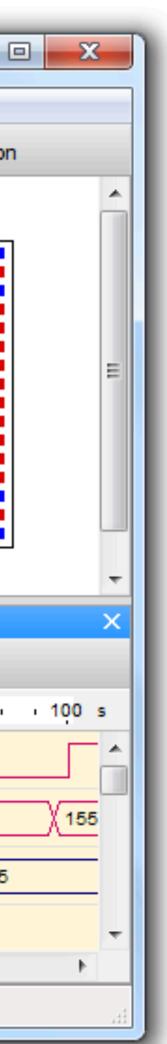

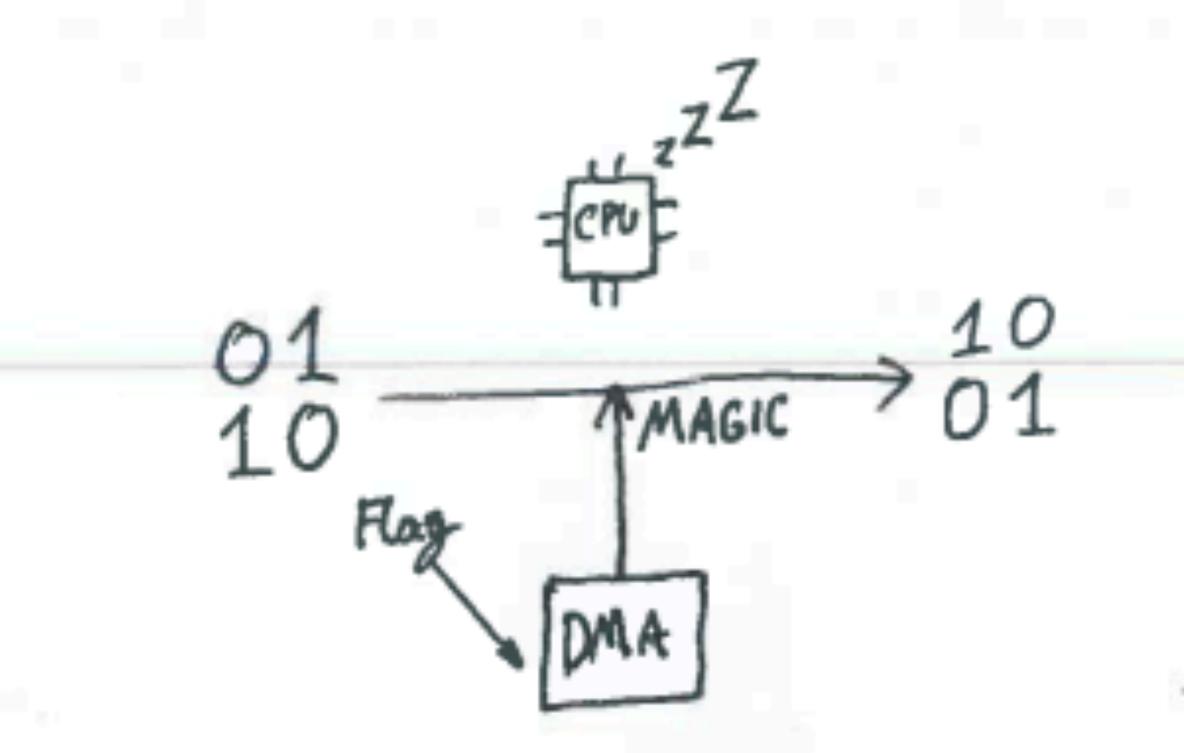

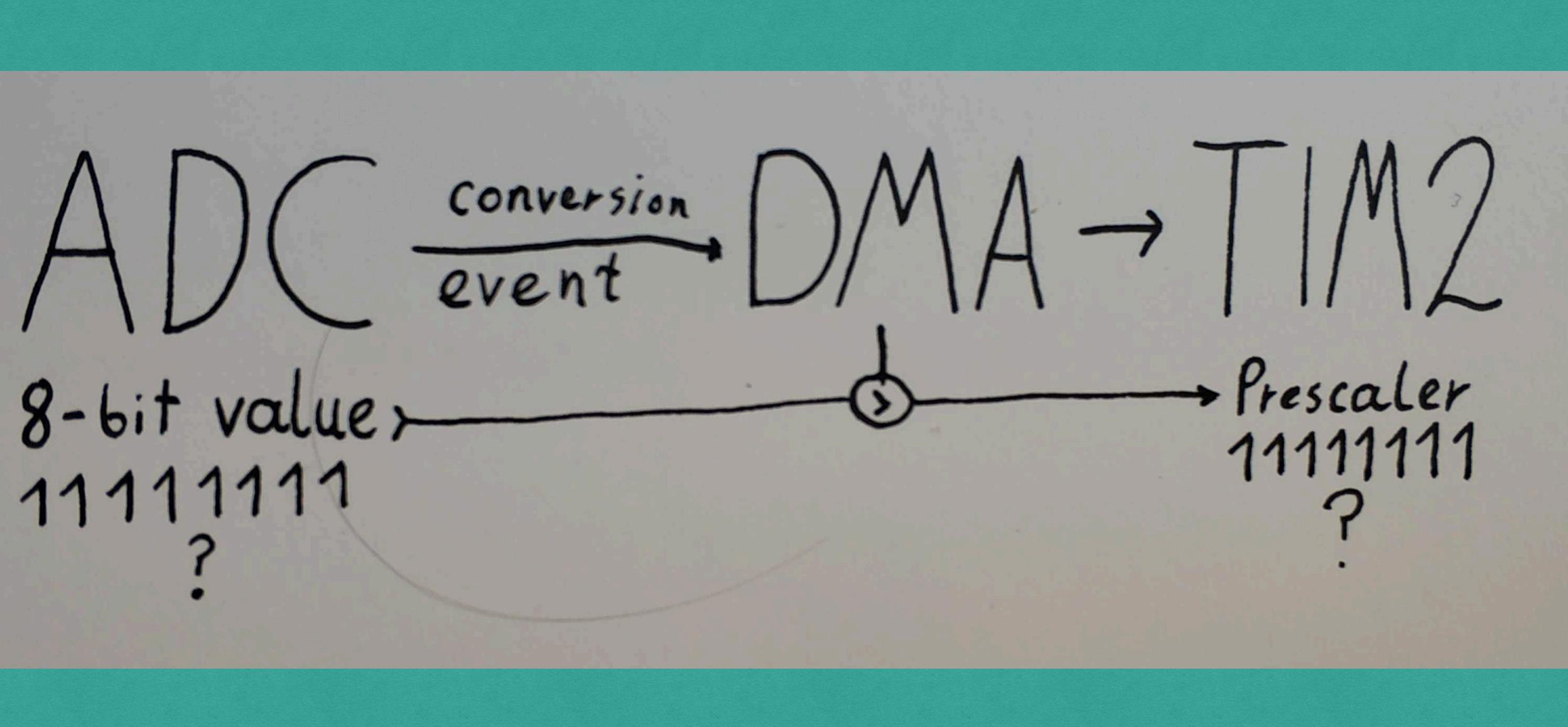

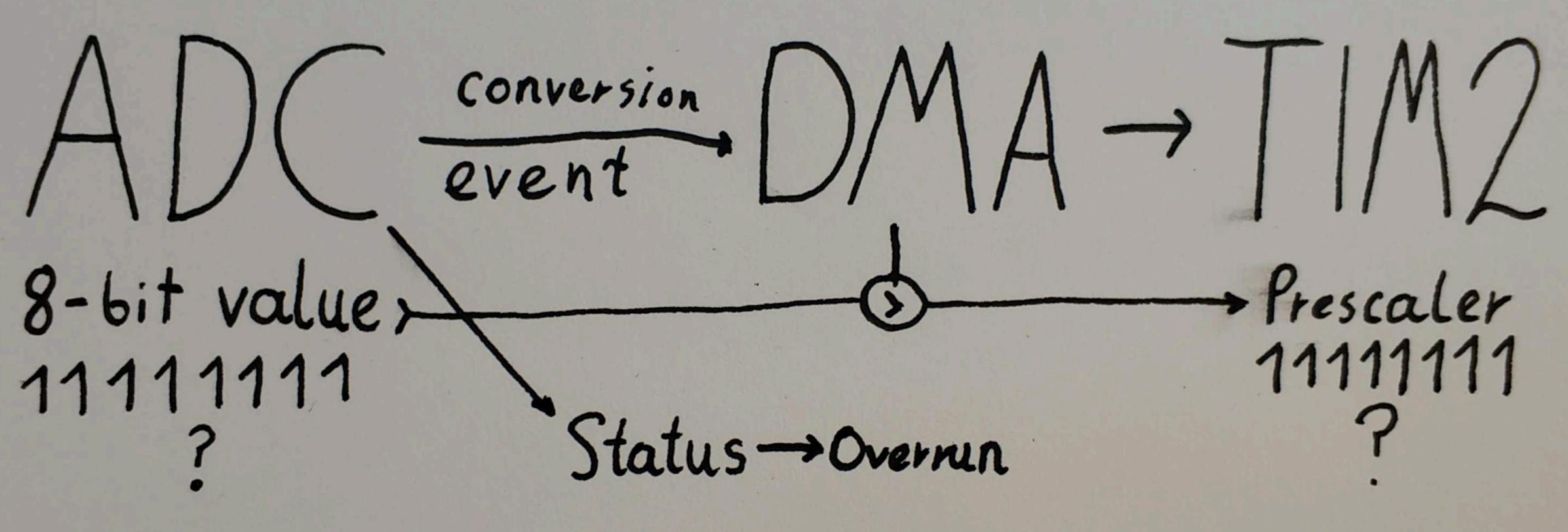

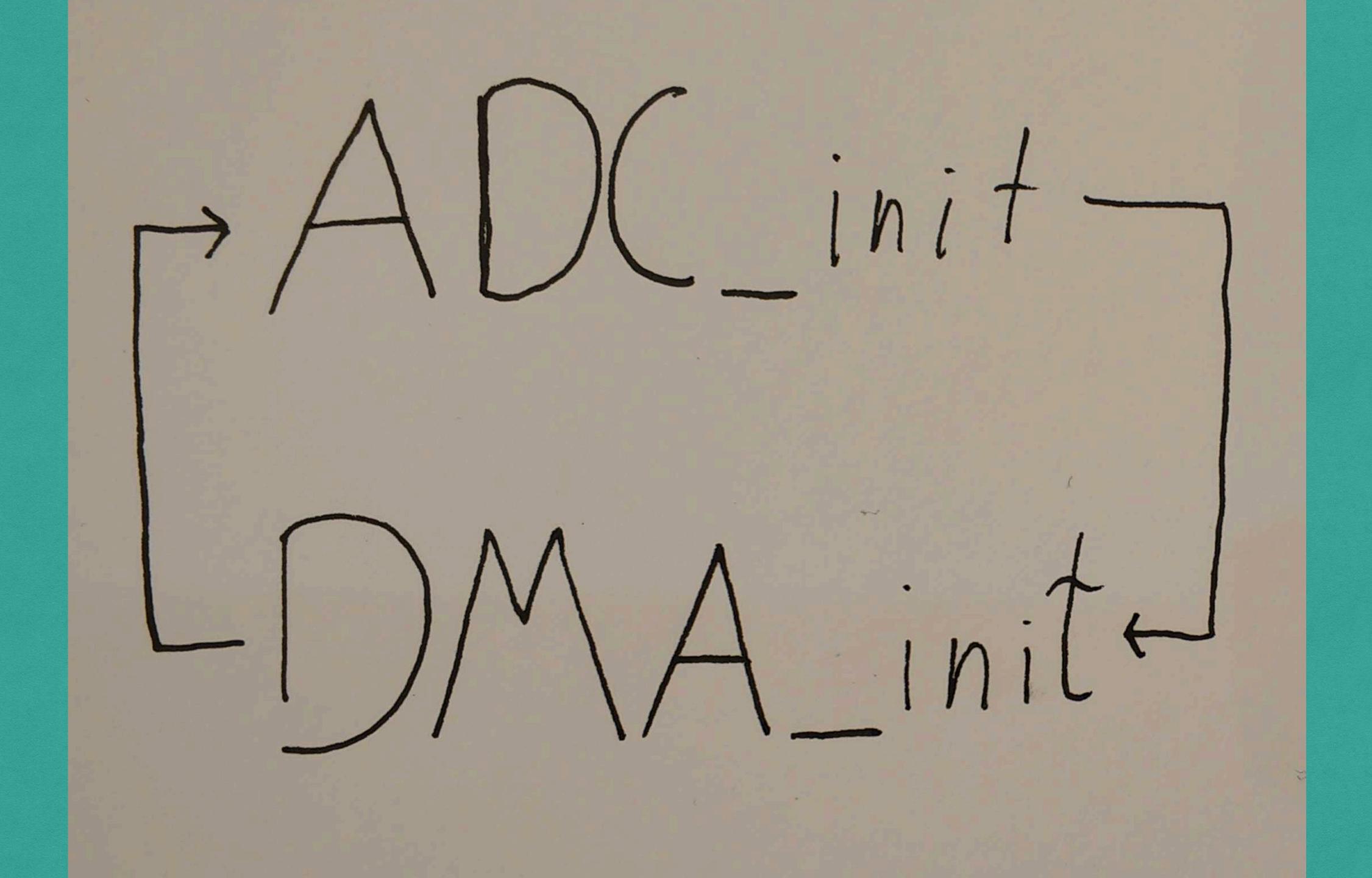

### ADC + DMA Configuration and problems

Digital Converter Analog 3.3V Mar ADC -> 255

DMA OFF MEMCPY -

## DIRECT MEMORY ACCESS

#### DMA ON

# 8-6it value, 1111111

## Prescaler 1111111

### Summary What should we remember from this presentation

#### Tools

#### **Common problems**

#### Tools

#### **Clion or VSCode**

Good IDE will help you develop code.

Debugging will help you pinpoint the issues and go over obstacles.

#### **OpenOCD/GDB**

#### CubeMX

Helps to set up projects for stm products family.

#### **Common Problems**

##

#### Set The Clock

All peripherals need their clock to be set before working on them.

#### **Check Registers**

Configuration and status registers may represent behaviour you didn't predict.

#### **Order of Operations**

Order of operations of registers may be crucial.

#### Organise Knowledge

Draw and organise your knowledge when learning.

#### Lurk More Documentation

Documentation has a lot of edge cases and behaviours saving days.

#### **Plan Things**

Understand what are you doing and why?

# Thank you!